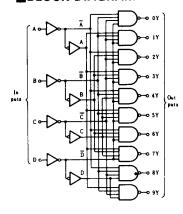

This monolithic decimal decoder consists of eight inverters and ten four-input NAND gates. The inverters are connected in pairs to make BCD input data available for decoding by NAND gates. Full decoding of valid input logic ensures that all outputs remain off for all invalid input conditions.

#### **■BLOCK DIAGRAM**

#### **INFUNCTION TABLE**

|         | BCD Input |   |   |   | Decimal Output |   |   |   |   |   |   |   |   |   |

|---------|-----------|---|---|---|----------------|---|---|---|---|---|---|---|---|---|

| No.     | D         | С | В | Α | 0              | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

| 0       | L         | L | L | L | L              | Н | Н | Н | Н | Н | Н | Н | Н | Н |

| 1       | L         | L | L | Н | Н              | L | Н | Н | Н | Н | Н | Н | Н | Н |

| 2       | L         | L | Н | L | Н              | Н | L | Н | Н | Н | Н | Н | Н | Н |

| 3       | L         | L | Н | Н | Н              | Н | Н | L | Н | Н | Н | Н | Н | Н |

| 4       | L         | Н | L | L | Н              | Н | Н | Н | L | Н | Н | Н | Н | Н |

| 5       | L         | Н | L | Н | Н              | Н | Н | Н | Н | L | H | Н | Н | Н |

| 6       | L         | Н | Н | L | Н              | Н | Н | Н | Н | Н | L | Н | Н | Н |

| 7       | L         | Н | Н | Н | Н              | Н | Н | Н | Н | Н | Н | L | Н | Н |

| 8       | Н         | L | L | L | Н              | Н | Н | Н | Н | Н | Н | Н | L | Н |

| 9       | Н         | L | L | Н | Н              | Н | H | н | Н | Н | Н | Н | Н | L |

|         | Н         | L | Н | L | Н              | Н | Н | Н | Н | Н | H | Н | Н | Н |

| INVALID | Н         | L | Н | H | Н              | Н | Н | Н | Н | Н | Н | Н | Н | Н |

|         | Н         | Н | L | L | Н              | Н | Н | н | Н | Н | Н | Н | Н | Н |

|         | Н         | Н | L | Н | Н              | Н | Н | Н | Н | Н | Н | Н | Н | Н |

|         | Н         | Н | Н | L | Н              | Н | Н | Н | H | Н | Н | Н | Н | Н |

|         | Н         | Н | Н | Н | Н              | Н | Н | Н | Н | Н | Н | Н | Н | Н |

H; high level, L; low level

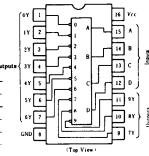

## **■PIN ARRANGEMENT**

# **ELECTRICAL CHARACTERISTICS** ( $Ta = -20 \sim +75^{\circ}C$ )

| Item                                       | Symbol | Test Conditions                                                                                     | min        | typ* | max  | Unit  |    |

|--------------------------------------------|--------|-----------------------------------------------------------------------------------------------------|------------|------|------|-------|----|

|                                            | VIH    |                                                                                                     |            | 2.0  |      | -     | V  |

| Input voltage                              | VIL    |                                                                                                     |            | -    | -    | 0.8   | V  |

|                                            | Vон    | $V_{CC} = 4.75 \text{ V}, V_{IH} = 2 \text{ V}, V_{IL} = 0.8 \text{ V}, I_{OH} = -400 \mu \text{A}$ |            | 2.7  | -    | -     | V  |

| Output voltage                             | Vol    | $V_{CC} = 4.75 \text{ V}, V_{IH} = 2 \text{ V}, V_{IL} = 0.8 \text{ V}$                             | Io L = 8mA | -    | _    | 0.5   | v  |

|                                            |        |                                                                                                     | IoL = 4mA  | -    |      | 0.4   |    |

|                                            | Iтн    | $V_{CC} = 5.25 \text{V},  V_I = 2.7 \text{V}$                                                       |            | -    | -    | 20    | μA |

| Input current                              | In     | $V_{CC} = 5.25 \text{V},  V_I = 0.4 \text{V}$                                                       | -          | _    | -0.4 | mA    |    |

|                                            | Iı .   | $V_{CC} = 5.25 \text{V},  V_I = 7 \text{V}$                                                         | _          | -    | 0.1  | mA    |    |

| Short-circuit output current Ios Vcc=5.25V |        |                                                                                                     |            | - 20 |      | - 100 | mA |

| Supply current                             | lcc**  | $V_{CC} = 5.25V$                                                                                    | -          | 7    | 13   | mA    |    |

| Input clamp voltage                        | Vik    | $V_{CC} = 4.75 \text{V},  I_{IN} = -18 \text{mA}$                                                   |            | _    | -    | -1.5  | V  |

<sup>\*</sup> VCC = 5V, Ta = 25°C

<sup>\*\*</sup> ICC is measured with all outputs open and all inputs grounded.

# **ESWITCHING CHARACTERISTICS** ( $V_{cc}=5V$ , $T_a=25^{\circ}C$ )

| Item                   | ·       | Symbol | Test Conditions                                    | min | typ | max | Unit |

|------------------------|---------|--------|----------------------------------------------------|-----|-----|-----|------|

|                        | 2 Stage | tРLН   | $C_L = 15 \mathrm{pF}, \ R_L = 2 \mathrm{k}\Omega$ | _   | 15  | 25  | ns   |

| n e di di e            | 3 Stage |        |                                                    | _   | 20  | 30  |      |

| Propagation delay time | 2 Stage | tрнL   |                                                    | -   | 15  | 25  | ns   |

|                        | 3 Stage |        |                                                    | _   | 20  | 30  |      |

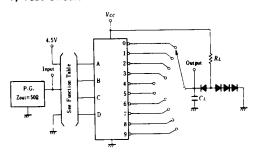

# **TESTING METHOD**

## 1) Test Circuit

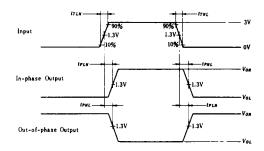

#### Waveform

Input pulse:  $t_{TLH} \le 15$ ns,  $t_{THL} \le 6$ ns, PRR = 1 MHz, duty cycle 50%.

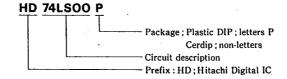

Factory orders for circuits described in this databook should include a three-part type number as explained in the following example.

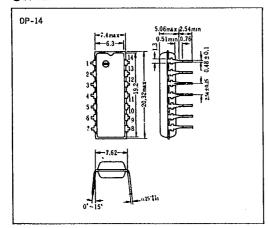

#### ■Plastic DIP

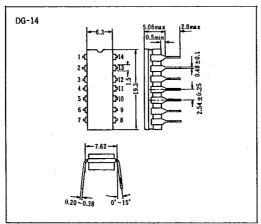

#### ●14 Pin

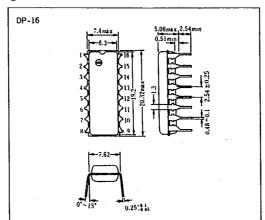

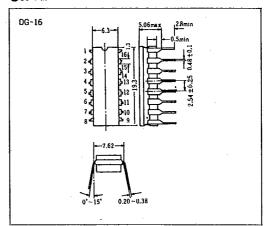

#### ●16 Pin

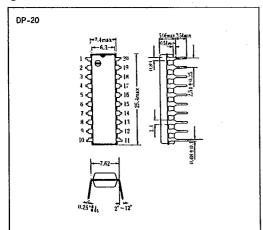

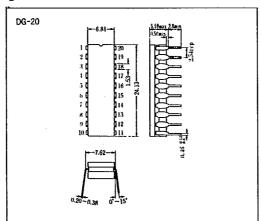

## ●20 Pin

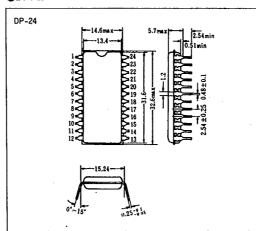

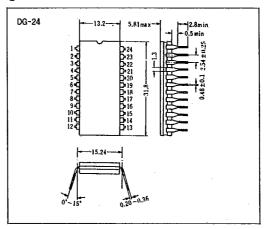

## ●24 Pin

## **■**Cerdip

# ●14 Pin

# ●16 Pin

# ●20 Pin

# ●24 Pin

# **@HITACHI**